陕西射频芯片数字模块物理布局

芯片设计模板是预先设计好的电路模块,它们可以被设计师重用和定制,以加速芯片设计的过程。设计模板可以包括常见的电路结构、接口、内存控制器等。使用设计模板可以减少设计时间和成本,提高设计的一致性和可重用性。随着芯片设计的复杂性增加,设计模板的使用变得越来越普遍。然而,设计模板的选择和定制需要考虑目标应用的具体要求,以确保终设计的性能和可靠性。设计模板的策略性使用可以提升设计效率,同时保持设计的创新性和灵活性。网络芯片在云计算、数据中心等场景下,确保了海量数据流的实时交互与传输。陕西射频芯片数字模块物理布局

芯片设计是一项且复杂的工程,它要求设计师在宏观和微观层面上都具备全局视角。在宏观层面,设计师必须洞察市场趋势,了解消费者需求,同时确保产品功能与现有技术生态的兼容性。这涉及到对市场进行深入分析,预测未来技术发展,并与产品管理团队紧密合作,以确保设计满足目标市场的需求。在微观层面,设计师则需要专注于晶体管的精确布局、电路设计的优化以及信号路径的精确规划,这些细节对芯片的性能有着直接的影响。成功的芯片设计必须在宏观与微观之间找到恰当的平衡点,这不要求设计师具备深厚的技术知识,还需要他们对市场动态有敏锐的洞察力和预测能力。浙江芯片一站式设计芯片前端设计完成后,进入后端设计阶段,重点在于如何把设计“画”到硅片上。

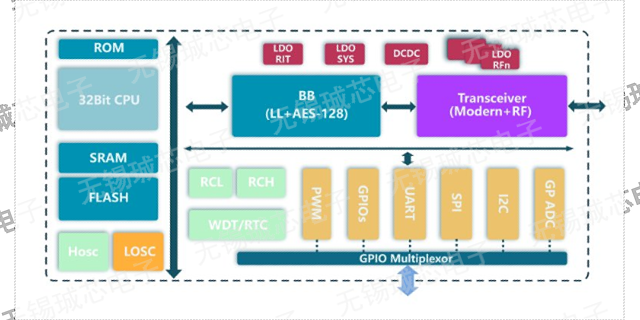

芯片中的射频芯片在无线通信领域扮演着至关重要的角色。它们负责处理无线信号的调制、解调以及放大等任务,是实现无线连接的重要。随着移动通信技术的快速发展,射频芯片的设计面临着更高的频率、更宽的带宽以及更强的抗干扰能力的挑战。5G技术的商用化对射频芯片提出了更高的要求,推动了射频芯片设计和制造技术的革新。射频芯片的小型化和集成化,使得它们能够适应紧凑的移动设备内部空间,同时保持高效的信号处理能力。这些进步不提升了无线通信的速度和质量,也为新兴的物联网(IoT)设备提供了强大的连接支持。

芯片运行功耗是芯片设计中的一个重要考虑因素,它直接影响到设备的电池寿命、散热需求和成本。随着芯片性能的不断提升,功耗管理变得越来越具有挑战性。设计师们采取多种策略来降低功耗,包括使用更低的电压、更高效的电路设计、动态电压频率调整(DVFS)和电源门控等技术。此外,新的制程技术如FinFET和FD-SOI也在帮助降低功耗。这些技术的应用不提高了芯片的性能,同时也使得设备更加节能,对于推动移动设备和高性能计算的发展具有重要作用。分析芯片性能时,还需评估其在不同工作条件下的稳定性与可靠性。

功耗管理在芯片设计中的重要性不言而喻,特别是在对能效有极高要求的移动设备和高性能计算领域。随着技术的发展和应用需求的增长,市场对芯片的能效比提出了更高的标准。芯片设计师们正面临着通过创新技术降低功耗的挑战,以满足这些不断变化的需求。 为了实现功耗的化,设计师们采用了多种先进的技术策略。首先,采用更先进的制程技术,如FinFET或FD-SOI,可以在更小的特征尺寸下集成更多的电路元件,从而减少单个晶体管的功耗。其次,优化电源管理策略,如动态电压频率调整(DVFS),允许芯片根据工作负载动态调整电源和时钟频率,以减少不必要的能耗。此外,使用低功耗设计技术,如电源门控和时钟门控,可以进一步降低静态功耗。同时,开发新型的电路架构,如异构计算平台,可以平衡不同类型处理器的工作负载,以提高整体能效。芯片的IO单元库设计须遵循行业标准,确保与其他芯片和PCB板的兼容性和一致性。湖北芯片前端设计

芯片行业标准随技术演进而不断更新,推动着半导体行业的技术创新与应用拓展。陕西射频芯片数字模块物理布局

在芯片设计中集成国密算法是一项挑战,它要求设计师在保障安全性的同时,尽量不影响芯片的性能。国密算法的运行会加大芯片的计算负担,可能导致处理速度下降和功耗增加。为了解决这一问题,设计师们采用了一系列策略,包括优化算法本身的效率、改进电路设计以减少资源消耗,以及采用高效的加密模式来降低对整体性能的负面影响。此外,随着安全威胁的不断演变,算法的更新和升级也变得尤为重要。设计师们必须构建灵活的硬件平台,以便于未来的算法更新,确保长期的安全性和芯片的适应性。陕西射频芯片数字模块物理布局