江西半导体封装载体联系方式

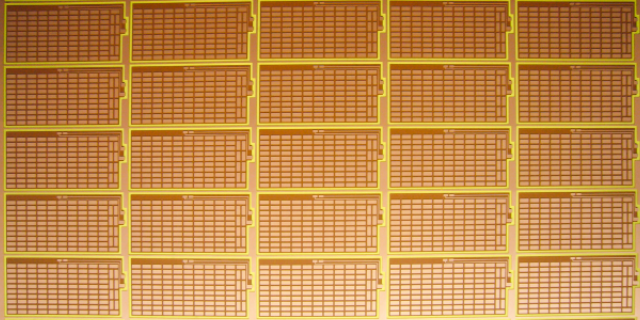

探索蚀刻在半导体封装中的3D封装组装技术研究,主要关注如何利用蚀刻技术实现半导体封装中的三维(3D)封装组装。

首先,需要研究蚀刻技术在3D封装组装中的应用。蚀刻技术可以用于去除封装结构之间的不需要的材料或层,以实现封装组件的3D组装。可以考虑使用湿蚀刻或干蚀刻,根据具体的组装需求选择合适的蚀刻方法。

其次,需要考虑蚀刻对封装结构的影响。蚀刻过程可能会对封装结构造成损伤,如产生裂纹、改变尺寸和形状等。因此,需要评估蚀刻工艺对封装结构的影响,以减少潜在的失效风险。

此外,需要研究蚀刻工艺的优化和控制。蚀刻工艺参数的选择和控制对于实现高质量的3D封装组装非常重要。需要考虑蚀刻剂的选择、浓度、温度、蚀刻时间等参数,并通过实验和优化算法等手段,找到适合的蚀刻工艺条件。

在研究3D封装组装中的蚀刻技术时,还需要考虑蚀刻过程的可重复性和一致性。确保蚀刻过程在不同的批次和条件下能够产生一致的结果,以便实现高效的生产和组装。综上所述,蚀刻在半导体封装中的3D封装组装技术研究需要综合考虑蚀刻技术的应用、对封装结构的影响、蚀刻工艺的优化和控制等多个方面。通过实验、数值模拟和优化算法等手段,可以实现高质量和可靠性的3D封装组装。 蚀刻技术:半导体封装中的精细加工利器!江西半导体封装载体联系方式

蚀刻工艺与半导体封装器件功能集成是一个重要的研究领域,旨在将蚀刻工艺与封装器件的功能需求相结合,实现性能优化和功能集成。

1. 通道形状控制:蚀刻工艺可以控制封装器件的通道形状,例如通过调制蚀刻剂的配方和蚀刻条件来实现微米尺寸的通道形状调控。这种蚀刻调控可以实现更高的流体控制和热传输效率,优化封装器件的性能。

2. 孔隙控制:蚀刻工艺可以通过控制蚀刻剂的浓度、温度和蚀刻时间等参数,实现对封装器件中孔隙形状和大小的控制。合理的孔隙设计可以提高封装器件的介电性能、热传导性和稳定性。

3。 电极形貌调控:蚀刻工艺可以用于调控封装器件中电极的形貌和结构,例如通过选择合适的蚀刻剂和蚀刻条件来实现电极的纳米级精细加工。这种电极形貌调控可以改善电极的界面特性和电流传输效率,提高封装器件的性能。

4. 保护层和阻隔层制备:蚀刻工艺可以用于制备封装器件中的保护层和阻隔层,提高器件的封装性能和可靠性。通过选择合适的蚀刻剂和工艺条件,可以实现保护层和阻隔层的高质量制备,并确保其与器件的良好兼容性。

总之,蚀刻工艺与半导体封装器件功能集成的研究旨在通过精确控制蚀刻工艺参数,实现对封装器件结构、形貌和性能的有效调控,以满足不同应用需求。 优势半导体封装载体共同合作蚀刻技术的奇妙之处!

蚀刻技术在半导体封装中一直是一个重要的制造工艺,但也存在一些新的发展和挑战。

高分辨率和高选择性:随着半导体器件尺寸的不断缩小,对蚀刻工艺的要求也越来越高。要实现更高的分辨率和选择性,需要开发更加精细的蚀刻剂和蚀刻工艺条件,以满足小尺寸结构的制备需求。

多层封装:多层封装是实现更高集成度和更小尺寸的关键。然而,多层封装也带来了新的挑战,如层间结构的蚀刻控制、深层结构的蚀刻难度等。因此,需要深入研究多层封装中的蚀刻工艺,并开发相应的工艺技术来克服挑战。

工艺控制和监测:随着蚀刻工艺的复杂性增加,需要更精确的工艺控制和实时监测手段。开发先进的工艺控制和监测技术,如反馈控制系统和实时表征工具,可以提高蚀刻工艺的稳定性和可靠性。

环境友好性:蚀刻工艺产生的废液和废气对环境造成影响。因此,开发更环保的蚀刻剂和工艺条件,以减少对环境的负面影响,是当前的研究方向之一。

总的来说,蚀刻技术在半导体封装中面临着高分辨率、多层封装、新材料和纳米结构、工艺控制和监测以及环境友好性等方面的新发展和挑战。解决这些挑战需要深入研究和创新,以推动蚀刻技术在半导体封装中的进一步发展。

在半导体封装中,蚀刻技术可以用于实现微米甚至更小尺寸的结构和器件制备。以下是一些常见的尺寸制备策略:

1. 基础蚀刻:基础蚀刻是一种常见的尺寸制备策略,通过选择合适的蚀刻剂和蚀刻条件,可以在半导体材料上进行直接的蚀刻,从而形成所需的结构和尺寸。这种方法可以实现直接、简单和高效的尺寸制备。

2. 掩蔽蚀刻:掩蔽蚀刻是一种利用掩膜技术进行尺寸制备的策略。首先,在待蚀刻的半导体材料上覆盖一层掩膜,然后通过选择合适的蚀刻剂和蚀刻条件,在掩膜上进行蚀刻,从而将所需的结构和尺寸转移到半导体材料上。这种方法可以实现更加精确和可控的尺寸制备。

3. 镀膜与蚀刻:镀膜与蚀刻是一种常见的尺寸制备策略,适用于需要更高精度的尺寸制备。首先,在待蚀刻的半导体材料上进行一层或多层的镀膜,然后通过选择合适的蚀刻剂和蚀刻条件,来蚀刻镀膜,从而得到所需的结构和尺寸。这种方法可以通过控制镀膜的厚度和蚀刻的条件,实现非常精确的尺寸制备。

总的来说,蚀刻技术在半导体封装中可以通过基础蚀刻、掩蔽蚀刻和镀膜与蚀刻等策略来实现尺寸制备。选择合适的蚀刻剂和蚀刻条件,结合掩膜技术和镀膜工艺,可以实现不同尺寸的结构和器件制备,满足不同应用需求。 探索半导体封装技术的发展趋势。

蚀刻技术对半导体封装的密封性能可以产生一定的影响,主要体现在以下几个方面的研究:

蚀刻表面形貌:蚀刻过程可能会导致封装器件表面的粗糙度变化。封装器件的表面粗糙度对封装密封性能有影响,因为较高的表面粗糙度可能会增加渗透性,并降低封装的密封性能。因此,研究蚀刻表面形貌对封装密封性能的影响,可以帮助改进蚀刻工艺,以实现更好的封装密封性能。

蚀刻后的残留物:蚀刻过程中可能会产生一些残留物,如蚀刻剂、气泡和颗粒等。这些残留物可能会附着在封装器件的表面,影响封装密封性能。

蚀刻对封装材料性能的影响:蚀刻过程中,化学物质可能会与封装材料发生反应,导致材料的性能变化。这可能包括材料的化学稳定性、机械强度、温度稳定性等方面的变化。研究蚀刻对封装材料性能的影响,可以帮助选择合适的封装材料,并优化蚀刻工艺,以实现更好的封装密封性能。

蚀刻对封装器件的气密性能的影响:封装器件的气密性能对于防止外界环境中的污染物进入内部关键部件至关重要。蚀刻过程中可能会对封装器件的气密性能产生一定的影响,特别是在使用湿式蚀刻方法时。研究蚀刻对封装器件的气密性能的影响,可以帮助优化蚀刻工艺,确保封装器件具备良好的气密性能。 蚀刻技术如何实现半导体封装中的仿真设计!吉林半导体封装载体检测

蚀刻技术如何实现半导体封装中的电路互联!江西半导体封装载体联系方式

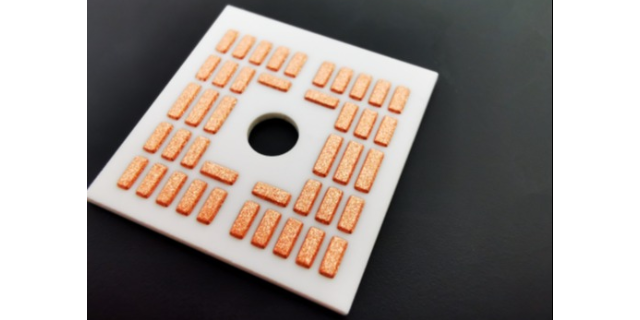

在射频和微波应用中,半导体封装载体的性能研究至关重要。以下是生产过程中注意到的一些可以进行研究的方向和关注点:

封装材料选择:封装材料的介电性能对信号传输和封装性能有很大影响。研究不同材料的介电常数、介质损耗和温度稳定性,选择合适的封装材料。

封装结构设计:射频和微波应用中,对信号的传输和耦合要求非常严格,封装结构设计需要考虑信号完整性、串扰、功率耗散等因素。研究封装结构的布线、分层、引线长度等参数的优化。

路由和布线规划:在高频应用中,信号的传输线要考虑匹配阻抗、信号完整性和串扰等问题。研究信号路由和布线规划的较优实践,优化信号的传输性能。

封装功耗和散热:对于高功率射频和微波应用,功耗和散热是关键考虑因素。研究封装的热导率、散热路径和散热结构,优化功率的传输和散热效果。

射频性能测试:封装载体在射频应用中的性能需要通过测试进行验证。研究射频性能测试方法和工具,评估封装载体的频率响应、S参数、噪声性能等指标。

射频封装可靠性:射频和微波应用对封装的可靠性要求高,因为封装载体可能在高温、高功率和高频率的工作条件下长时间运行。研究封装材料的热膨胀系数、疲劳寿命和可靠性预测方法,提高封装的可靠性。

江西半导体封装载体联系方式

上一篇: 多功能半导体封装载体材料

下一篇: 四川多功能半导体封装载体