特点半导体封装载体规范

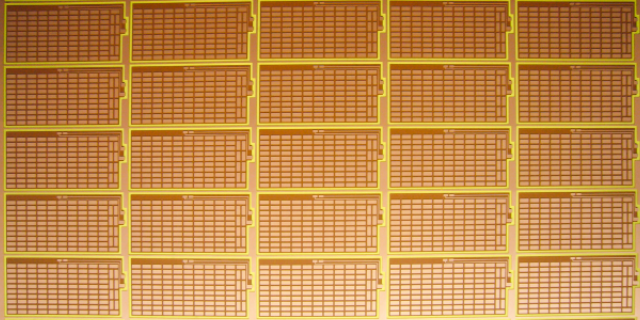

在三维封装中,半导体封装载体的架构优化研究主要关注如何提高封装载体的性能、可靠性和制造效率,以满足日益增长的电子产品对高密度封装和高可靠性的需求。

1. 材料选择和布局优化:半导体封装载体通常由有机基板或无机材料制成。优化材料选择及其在载体上的布局可以提高载体的热导率、稳定性和耐久性。

2. 电气和热传导优化:对于三维封装中的多个芯片堆叠,优化电气和热传导路径可以提高整个封装系统的性能。通过设计导热通道和优化电路布线,可以降低芯片温度、提高信号传输速率和降低功耗。

3. 结构强度和可靠性优化:三维封装中的芯片堆叠会产生较大的应力和振动,因此,优化载体的结构设计,提高结构强度和可靠性是非常重要的。

4. 制造工艺优化:对于三维封装中的半导体封装载体,制造工艺的优化可以提高制造效率和降低成本。例如,采用先进的制造工艺,如光刻、薄在进行三维封装时,半导体封装载体扮演着重要的角色,对于架构的优化研究可以提高封装的性能和可靠性。

这些研究方向可以从不同角度对半导体封装载体的架构进行优化,提高封装的性能和可靠性,满足未来高性能和高集成度的半导体器件需求。 蚀刻技术:半导体封装中的精密控制工艺!特点半导体封装载体规范

在射频和微波应用中,半导体封装载体的性能研究至关重要。以下是生产过程中注意到的一些可以进行研究的方向和关注点:

封装材料选择:封装材料的介电性能对信号传输和封装性能有很大影响。研究不同材料的介电常数、介质损耗和温度稳定性,选择合适的封装材料。

封装结构设计:射频和微波应用中,对信号的传输和耦合要求非常严格,封装结构设计需要考虑信号完整性、串扰、功率耗散等因素。研究封装结构的布线、分层、引线长度等参数的优化。

路由和布线规划:在高频应用中,信号的传输线要考虑匹配阻抗、信号完整性和串扰等问题。研究信号路由和布线规划的较优实践,优化信号的传输性能。

封装功耗和散热:对于高功率射频和微波应用,功耗和散热是关键考虑因素。研究封装的热导率、散热路径和散热结构,优化功率的传输和散热效果。

射频性能测试:封装载体在射频应用中的性能需要通过测试进行验证。研究射频性能测试方法和工具,评估封装载体的频率响应、S参数、噪声性能等指标。

射频封装可靠性:射频和微波应用对封装的可靠性要求高,因为封装载体可能在高温、高功率和高频率的工作条件下长时间运行。研究封装材料的热膨胀系数、疲劳寿命和可靠性预测方法,提高封装的可靠性。

山西半导体封装载体规范蚀刻技术如何保证半导体封装的一致性!

低成本半导体封装载体的制备及性能优化针对成本控制的要求,研究如何制备价格低廉的封装载体,并优化其性能以满足产品需求。

1. 材料选择与设计:选择成本较低的材料,如塑料、有机材料等,同时设计和优化材料的组合和结构,以满足封装载体的性能和可靠性要求。

2. 制造工艺优化:通过改进制造工艺,提高生产效率和降低生产成本。例如,采用高通量生产技术、自动化流程等,减少人力和时间投入,降低生产成本。

3. 资源循环利用:通过回收和再利用废料和废弃物,降低原材料消耗和废弃物处理成本。例如,利用废料进行再生加工,将废弃物转化为资源。

4. 设备优化与控制:优化设备性能和控制策略,提高生产效率和质量稳定性,降低成本。例如,采用精密调控技术,减少材料的浪费和损耗。

5. 可靠性与性能评估:进行系统可靠性和性能评估,优化封装载体的设计和制造过程,确保其符合产品的性能要求,并提供高质量的封装解决方案。

低成本半导体封装载体的制备及性能优化研究对于降低产品成本、提高市场竞争力具有重要意义。需要综合考虑材料选择、制造工艺优化、资源循环利用、设备优化与控制等方面,通过技术创新和流程改进,实现低成本封装载体的制备,并保证其性能和可靠性。

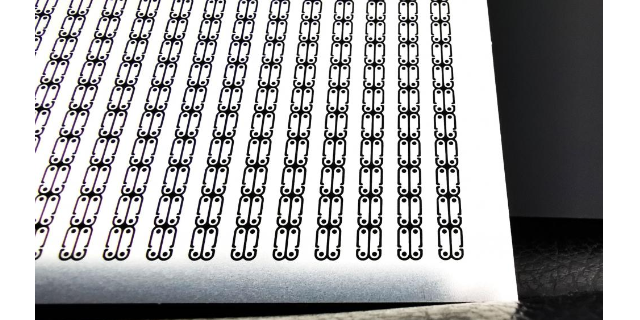

在半导体封装中,蚀刻技术可以用于实现微米甚至更小尺寸的结构和器件制备。以下是一些常见的尺寸制备策略:

1. 基础蚀刻:基础蚀刻是一种常见的尺寸制备策略,通过选择合适的蚀刻剂和蚀刻条件,可以在半导体材料上进行直接的蚀刻,从而形成所需的结构和尺寸。这种方法可以实现直接、简单和高效的尺寸制备。

2. 掩蔽蚀刻:掩蔽蚀刻是一种利用掩膜技术进行尺寸制备的策略。首先,在待蚀刻的半导体材料上覆盖一层掩膜,然后通过选择合适的蚀刻剂和蚀刻条件,在掩膜上进行蚀刻,从而将所需的结构和尺寸转移到半导体材料上。这种方法可以实现更加精确和可控的尺寸制备。

3. 镀膜与蚀刻:镀膜与蚀刻是一种常见的尺寸制备策略,适用于需要更高精度的尺寸制备。首先,在待蚀刻的半导体材料上进行一层或多层的镀膜,然后通过选择合适的蚀刻剂和蚀刻条件,来蚀刻镀膜,从而得到所需的结构和尺寸。这种方法可以通过控制镀膜的厚度和蚀刻的条件,实现非常精确的尺寸制备。

总的来说,蚀刻技术在半导体封装中可以通过基础蚀刻、掩蔽蚀刻和镀膜与蚀刻等策略来实现尺寸制备。选择合适的蚀刻剂和蚀刻条件,结合掩膜技术和镀膜工艺,可以实现不同尺寸的结构和器件制备,满足不同应用需求。 控制半导体封装技术中的热和电磁干扰。

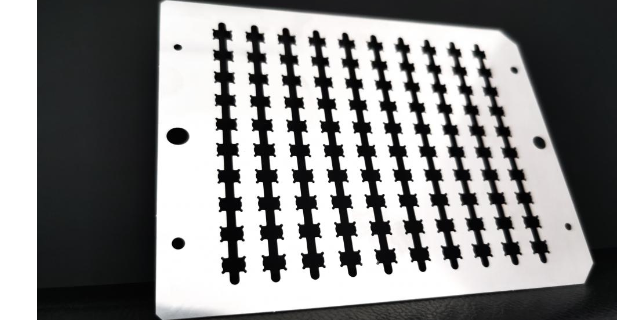

蚀刻是一种制造过程,通过将物质从一个固体材料表面移除来创造出所需的形状和结构。在三维集成封装中,蚀刻可以应用于多个方面,并且面临着一些挑战。

应用:模具制造:蚀刻可以用于制造三维集成封装所需的模具。通过蚀刻,可以以高精度和复杂的结构制造出模具,以满足集成封装的需求。管理散热:在三维集成封装中,散热是一个重要的问题。蚀刻可以用于制造散热器,蚀刻在三维集成封装中的应用与挑战是一个值得探索的领域。

在应用蚀刻技术的同时,也面临着一些挑战。

挑战:首先,蚀刻技术的精确性是一个重要的挑战。因为三维集成封装中的微细结构非常小,所以需要实现精确的蚀刻加工。这涉及到蚀刻工艺的优化和控制,以确保得到设计要求的精确结构。其次,蚀刻过程中可能会产生一些不良影响,如侵蚀和残留物。这可能会对电路板的性能和可靠性产生负面影响。因此,需要开发新的蚀刻工艺和处理方法,以避免这些问题的发生。蚀刻技术还需要与其他工艺相互配合,如电镀和蚀刻后的清洗等。这要求工艺之间的协调和一体化,以确保整个制造过程的质量与效率。

综上所述,只有通过不断地研究和创新,克服这些挑战,才能进一步推动蚀刻技术在三维集成封装中的应用。 半导体封装技术中的热管理和电力传输。特点半导体封装载体规范

高可靠性封装技术在半导体行业的应用。特点半导体封装载体规范

蚀刻是一种常用的制造半导体封装载体的工艺方法,它的主要优势包括:

1. 高精度:蚀刻工艺能够实现较高的精度和细致的图案定义,可以制造出非常小尺寸的封装载体,满足高密度集成电路的要求。

2. 灵活性:蚀刻工艺可以根据需求进行定制,可以制造出各种形状和尺寸的封装载体,适应不同的封装需求。

3. 高效性:蚀刻工艺通常采用自动化设备进行操作,可以实现批量生产和高效率的制造过程。

4. 一致性:蚀刻工艺能够对封装载体进行均匀的刻蚀处理,保证每个封装载体的尺寸和形状具有一致性,提高产品的稳定性和可靠性。

5. 优良的封装性能:蚀刻工艺能够制造出平整的封装载体表面,提供良好的金属连接和密封性能,保护半导体芯片不受外界环境的干扰,提高封装的可靠性。

总的来说,蚀刻工艺在制造半导体封装载体中具有高精度、灵活性、高效性和优良的封装性能等优势,能够满足封装需求并提高产品质量和可靠性。 特点半导体封装载体规范

上一篇: 湖南引线框架代加工

下一篇: 山西半导体封装载体规范