福建大规模半导体封装载体

蚀刻对半导体封装材料性能的影响与优化主要涉及以下几个方面:

表面粗糙度:蚀刻过程可能会引起表面粗糙度的增加,尤其是对于一些材料如金属。通过优化蚀刻工艺参数,如选择合适的蚀刻液、控制工艺参数和引入表面处理等,可以减少表面粗糙度增加的影响。

刻蚀深度的控制:蚀刻过程中,刻蚀深度的控制非常关键。过度刻蚀可能导致材料损坏或形状变化,而刻蚀不足则无法满足设计要求。优化工艺参数、实时监控蚀刻深度以及利用自动化控制系统可以实现更准确的刻蚀深度控制。

结构形貌:蚀刻过程可能对材料的结构形貌产生影响,尤其对于一些多层结构或异质结构材料。通过合理选择刻蚀液、优化蚀刻时间和温度等蚀刻工艺参数,可以使得材料的结构形貌保持良好,避免结构变形或破坏。

材料表面特性:蚀刻过程也可能改变材料表面的化学组成或表面能等特性。在蚀刻过程中引入表面处理或使用特定的蚀刻工艺参数可以优化材料表面的特性,例如提高润湿性或增强化学稳定性。

化学残留物:蚀刻过程中的化学液体和残留物可能对材料性能产生负面影响。合理选择蚀刻液、完全去除残留物以及进行适当的清洗等操作有助于减少化学残留物对材料性能的影响。

蚀刻技术带来半导体封装中的高可靠性!福建大规模半导体封装载体

蚀刻是一种制造过程,通过将物质从一个固体材料表面移除来创造出所需的形状和结构。在三维集成封装中,蚀刻可以应用于多个方面,并且面临着一些挑战。

应用:模具制造:蚀刻可以用于制造三维集成封装所需的模具。通过蚀刻,可以以高精度和复杂的结构制造出模具,以满足集成封装的需求。管理散热:在三维集成封装中,散热是一个重要的问题。蚀刻可以用于制造散热器,蚀刻在三维集成封装中的应用与挑战是一个值得探索的领域。

在应用蚀刻技术的同时,也面临着一些挑战。

挑战:首先,蚀刻技术的精确性是一个重要的挑战。因为三维集成封装中的微细结构非常小,所以需要实现精确的蚀刻加工。这涉及到蚀刻工艺的优化和控制,以确保得到设计要求的精确结构。其次,蚀刻过程中可能会产生一些不良影响,如侵蚀和残留物。这可能会对电路板的性能和可靠性产生负面影响。因此,需要开发新的蚀刻工艺和处理方法,以避免这些问题的发生。蚀刻技术还需要与其他工艺相互配合,如电镀和蚀刻后的清洗等。这要求工艺之间的协调和一体化,以确保整个制造过程的质量与效率。

综上所述,只有通过不断地研究和创新,克服这些挑战,才能进一步推动蚀刻技术在三维集成封装中的应用。 什么是半导体封装载体技术半导体封装技术中的热管理和电力传输。

蚀刻是一种半导体封装器件制造过程,用于制造电子元件的金属和介质层。然而,蚀刻过程会对器件的电磁干扰(EMI)性能产生一定的影响。

封装器件的蚀刻过程可能会引入导线间的电磁干扰,从而降低信号的完整性。这可能导致信号衰减、时钟偏移和误码率的增加。且蚀刻过程可能会改变器件内的互联距离,导致线路之间的电磁耦合增加。这可能导致更多的互模干扰和串扰。此外,蚀刻可能会改变器件的地线布局,从而影响地线的分布和效果。地线的布局和连接对于电磁干扰的抑制至关重要。如果蚀刻过程不当,地线的布局可能会受到破坏,导致电磁干扰效果不佳。还有,蚀刻过程可能会引入辐射噪声源,导致电磁辐射干扰。这可能对其他器件和系统产生干扰,影响整个系统的性能。

为了减小蚀刻对半导体封装器件的EMI性能的影响,可以采取以下措施:优化布线和引脚布局,减小信号线之间的间距,降低电磁耦合。优化地线布局和连接,确保良好的接地,降低地线回流电流。使用屏蔽材料和屏蔽技术来减小信号干扰和辐射。进行EMI测试和分析,及早发现和解决潜在问题。

总之,蚀刻过程可能会对半导体封装器件的EMI性能产生影响,但通过优化设计和采取相应的措施,可以减小这种影响,提高系统的EMI性能。

利用蚀刻技术实现半导体封装的先进方法有以下几种:

1. 塑料光阻蚀刻:将光阻涂覆在半导体器件表面,利用紫外线曝光将光阻区域暴露,通过化学溶液将光刻图案外的光阻溶解,暴露出需要刻蚀的区域,然后使用化学蚀刻液对半导体器件进行刻蚀。

2. 基板蚀刻:将待封装的半导体芯片放置在特定的化学溶液中,通过化学反应溶解掉芯片上不需要的区域。这种腐蚀方法常用于制作开窗孔或切口。

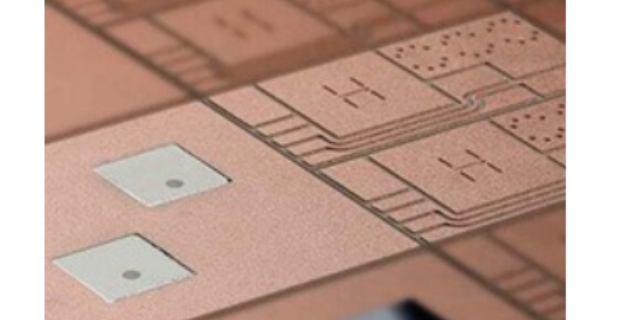

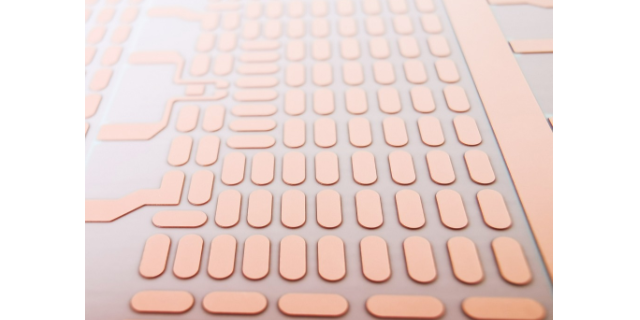

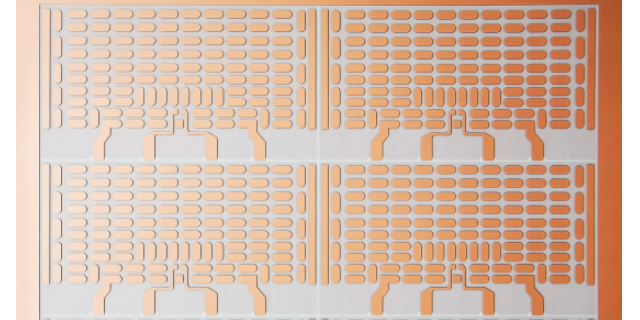

3. 金属蚀刻:在半导体封装过程中,需要用到金属材料(如铜、铝等)制作封装元件。利用化学蚀刻技术,将金属表面暴露在刻蚀液中,刻蚀液会将不需要的金属材料迅速溶解掉,从而形成所需的金属结构。

4. 导电蚀刻:将具有电导性的液体浸泡在待蚀刻的区域,利用电流通过蚀刻液与半导体器件之间建立电化学反应,使得不需要的材料通过阳极溶解,从而实现精确的蚀刻。这些是利用化学蚀刻技术实现半导体封装的一些先进方法,根据具体的封装需求和材料特性,可以选择适合的方法来实现半导体封装过程中所需的蚀刻作业。 半导体封装技术中的封装材料和工艺。

半导体封装载体中的信号传输与电磁兼容性研究是指在半导体封装过程中,针对信号传输和电磁兼容性的需求,研究如何优化信号传输和降低电磁干扰,确保封装器件的可靠性和稳定性。

1. 信号传输优化:分析信号传输路径和布线,优化信号线的走向、布局和长度,以降低信号传输中的功率损耗和信号失真。

2. 电磁兼容性设计:设计和优化封装载体的结构和屏蔽,以减少或屏蔽电磁辐射和敏感性。采用屏蔽罩、屏蔽材料等技术手段,提高封装器件的电磁兼容性。

3. 电磁干扰抑制技术:研究和应用抑制电磁干扰的技术,如滤波器、隔离器、电磁屏蔽等,降低封装载体内外电磁干扰的影响。通过优化封装结构和设计,提高器件的抗干扰能力。

4. 模拟仿真与测试:利用模拟仿真工具进行信号传输和电磁兼容性的模拟设计与分析,评估封装载体的性能。进行实验室测试和验证,确保设计的有效性和可靠性。

需要综合考虑信号传输优化、电磁兼容性设计、电磁干扰抑制技术、模拟仿真与测试、标准遵循与认证等方面,进行系统设计和优化,以提高封装载体的抗干扰能力和电磁兼容性,确保信号的传输质量和器件的稳定性。 封装技术对半导体芯片的保护和信号传输的重要性。江西半导体封装载体咨询问价

蚀刻技术:半导体封装中的精细加工利器!福建大规模半导体封装载体

功能性半导体封装载体的设计与制造研究是指在半导体封装领域,针对特定功能需求,研究和开发具有特定功能的封装载体,并进行相关制造工艺的研究。

1. 功能集成设计:根据特定功能的要求,设计封装载体中的功能单元、传感器、天线等,实现系统级集成,并与封装载体相连接。

2. 多功能性材料研究:研究和使用具有多功能性能的材料,如高导热材料、低介电常数材料、光学材料等,以满足封装载体在不同功能下的要求。

3. 高性能封装工艺研究:开发适合特定功能要求的封装工艺,并优化工艺参数、工艺流程等,以实现高性能的功能性封装载体。

4. 集成电路与器件优化设计:结合封装载体的具体功能需求,优化集成电路和器件的设计,以实现更好的系统性能和可靠性。

5. 制造工艺控制与质量验证:通过制造工艺的优化和控制,确保功能性封装载体的质量和稳定性。进行相关测试和验证,验证载体的功能性能和可靠性。

功能性半导体封装载体的设计与制造研究对于满足特定功能需求的封装载体的发展具有重要意义。需要综合考虑功能集成设计、多功能性材料研究、高性能封装工艺研究、集成电路与器件优化设计、制造工艺控制与质量验证等方面,进行综合性的研究与开发,以实现功能性封装载体的设计与制造。 福建大规模半导体封装载体

上一篇: 半导体封装载体私人定做

下一篇: 上海推广VCM弹片