重庆MEMS封装技术

PoP封装技术有以下几个有点:1)存储器件和逻辑器件可以单独地进行测试或替换,保障了良品率;2)双层POP封装节省了基板面积, 更大的纵向空间允许更多层的封装;3)可以沿PCB的纵向将Dram,DdramSram,Flash,和 微处理器进行混合装联;4)对于不同厂家的芯片, 提供了设计灵活性,可以简单地混合装联在一起以满足客户的需求,降低了设计的复杂性和成本;5)目前该技术可以取得在垂直方向进行层芯片外部叠加装联;6)顶底层器件叠层组装的电器连接,实现了更快的数据传输速率,可以应对逻辑器件和存储器件之间的高速互联。SIP工艺流程划分,SIP封装制程按照芯片与基板的连接方式可分为引线键合封装和倒装焊两种。重庆MEMS封装技术

SMT制程在SIP工艺流程中的三部分都有应用:1st SMT PCB贴片 + 3rd SMT FPC贴镍片 + 4th SMT FPC+COB。SiP失效模式和失效机理,主要失效模式:(1) 焊接异常:IC引脚锡渣、精密电阻连锡。Ø 原因分析:底部UF (Underfill底部填充)胶填充不佳,导致锡进入IC引脚或器件焊盘间空洞造成短路。(2) 机械应力损伤:MOS芯片、电容裂纹。Ø 原因分析:(1) SiP注塑后固化过程产生的应力;(2)设备/治具产生的应力。(3) 过电应力损伤:MOS、电容等器件EOS损伤。Ø 原因分析:PCM SiP上的器件受电应力损伤(ESD、测试设备浪涌等)。重庆MEMS封装技术SiP 可将不同的材料,兼容不同的GaAs,Si,InP,SiC,陶瓷,PCB等多种材料进行组合进行一体化封装。

由于物联网“智慧”设备的快速发展,业界对能够在更小的封装内实现更多功能的系统级封装 (SiP) 器件的需求高涨,这种需求将微型化趋势推向了更高的层次:使用更小的元件和更高的密度来进行组装。 无源元件尺寸已从 01005 ( 0.4 mm× 0.2 mm) 缩小到 008004( 0.25 mm×0.125 mm) ,细间距锡膏印刷对 SiP 的组装来说变得越来越有挑战性。 对使用不同助焊剂和不同颗粒尺寸锡粉的 3 种锡膏样本进行了研究; 同时通过比较使用平台和真空的板支撑系统,试验了是否可以单独使用平台支撑来获得一致性较好的印刷工艺;并比较了激光切割和电铸钢网在不同开孔尺寸下的印刷结果。

电镀镍金:电镀是指借助外界直流电的作用,在溶液中进行电解反应,是导电体(例如金属)的表面趁机金属或合金层。电镀分为电镀硬金和软金工艺,镀硬金与软金的工艺基本相同,槽液组成也基本相同,区别是硬金槽内添加了一些微量金属镍或钴或铁等元素,由于电镀工艺中镀层金属的厚度和成分容易控制,并且平整度优良,所以在采用键合工艺的封装基板进行表面处理时,一般采用电镀镍金工艺,铝线的键合一般采用硬金,金线的键合一般都用软金。SiP封装基板具有薄形化、高密度、高精度等技术特点。

包装,主要目的是保证运输过程中的产品安全,及长期存放时的产品可靠性。对包装材料的强度、重量、温湿度特性、抗静电性能都有一定的要求。主要材料有Tray盘,抗静电袋,干燥剂、湿度卡,纸箱等。包装完毕后,直接入库或按照要求装箱后直接发货给客户。倒装焊封装工艺工序介绍,焊盘再分布,为了增加引线间距并满足倒装焊工艺的要求,需要对芯片的引线进行再分布。制作凸点,焊盘再分布完成之后,需要在芯片上的焊盘添加凸点,焊料凸点制作技术可采用电镀法、化学镀法、蒸发法、置球法和焊膏印尽4法。目前仍以电镀法较为普遍,其次是焊膏印刷法。据报告,2022年,SiP系统级封装市场总收入达到212亿美元。四川WLCSP封装行价

SOC与SIP都是将一个包含逻辑组件、内存组件、甚至包含无源组件的系统,整合在一个单位中。重庆MEMS封装技术

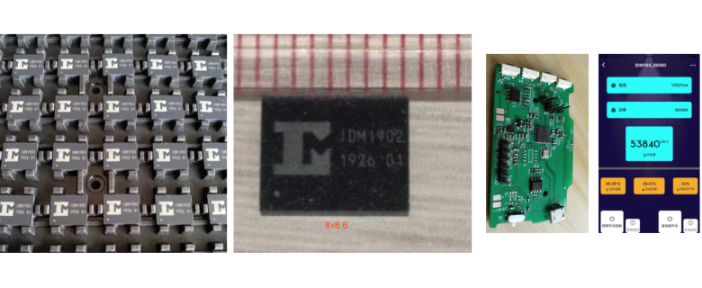

SiP芯片成品的制造过程,系统级封装(SiP)技术种类繁多,本文以双面塑封SiP产品为例,简要介绍SiP芯片成品的制造过程。SiP封装通常在一块大的基板上进行,每块基板可以制造几十到几百颗SiP成品。无源器件贴片,倒装芯片封装(Flip Chip)贴片——裸片(Die)通过凸点(Bump)与基板互连,回流焊接(正面)——通过控制加温熔化封装锡膏达到器件与基板间的键合焊线,键合(Wire Bond)——通过细金属线将裸片与基板焊盘连接塑封(Molding)——注入塑封材料包裹和保护裸片及元器件。重庆MEMS封装技术

上一篇: 广东防爆特种封装工艺

下一篇: 南通PCBA贴片厂EAP系统设计