江西防爆特种封装定制

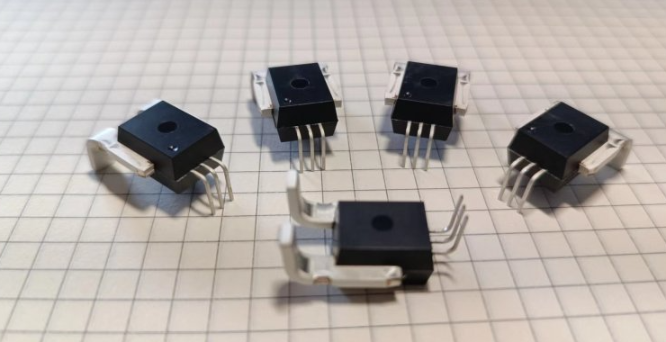

IGBT封装工艺流程,IGBT模块封装流程简介,1、丝网印刷:将锡膏按设定图形印刷于散热底板和DBC铜板表面,为自动贴片做好前期准备 印刷效果;2、自动贴片:将IGBT芯片与FRED芯片贴装于DBC印刷锡膏表面;IGBT封装环节包括:丝网印、贴片、键合、功能测试等环节。这其中任何一个看似简单的环节,都需要高水准的封装技术和设备配合完成。例如贴片环节,将IGBT芯片与FRED芯片贴装于DBC印刷锡膏表面。这个过程需要对IGBT芯片进行取放,要确保贴片良率和效率,就要求以电机为主要的贴片机具有高速、高频、高精力控等特点。PGA 封装是一种陶瓷封装方式,通常用于高频、高功率的场合。江西防爆特种封装定制

QFN的主要特点有:表面贴装封装、无引脚焊盘设计占有更小的PCB面积、组件非常薄(<1mm),可满足对空间有严格要求的应用、非常低的阻抗、自感,可满足高速或者微波的应用、具有优异的热性能,主要是因为底部有大面积散热焊盘、重量轻,适合便携式应用、无引脚设计。你可以模糊地把它看成一种缩小的PLCC封装,我们以32引脚的QFN与传统的28引脚 的PLCC封装比较为例,面积(5mm×5mm)缩小了84%,厚度(0.9mm)降低了80%,重量(0.06g)减轻了95%,电子封装寄生效应也降低了50%,所以,非常适合应用在手机、数码相机、PDA以及其它便携式小型电子设备的高密度印刷电路板上。河北半导体芯片特种封装SOP (Small Outline Package),SOP 封装是一种塑料封装方式,通常用于低频、低功率的场合。

目前,引线键合技术因成本相对低廉,仍是主流的封装互联技术,但它不适合对高密度、高 频有要求的产品。倒装焊接技术适合对高密度、高频及大电流有要求的产品,如电源管理、智能 终端的处理器等。TAB 封装技术主要应用于大规模、多引线的集成电路的封装。半导体(包括集成电路和分立器件)其芯片的封装已经历了好几代的变迁,从DIP、SOP、QFP、PGA、BGA到MCP再到SIP,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。封装(Package)可谓种类繁多,而且每一种封装都有其独特的地方,即它的优点和不足之处,当然其所用的封装材料、封装设备、封装技术根据其需要而有所不同。

cpu有两种封装形式?包括两种封装形式DIP封装和BGA封装。DIP封装,DIP封装(Dual In-line Package),又称双列直接包装技术,是指采用双列直接包装的集成电路芯片,绝大多数中小型集成电路采用这种包装形式,其引脚数量一般不超过 100。DIP封装的CPU芯片有两排引脚,需要插入DIP芯片插座上的结构。当然,也可以直接插在电路板上进行焊接,具有相同的焊孔数和几何排列。DIP从芯片插座上插入封装芯片时要特别小心,以免损坏管脚。DIP封装结构有:多层陶瓷双排直插式DIP,双列直插式单层陶瓷DIP,引线框架式DIP(包括玻璃陶瓷封接式、塑料封接式、陶瓷低熔玻璃封接式)等。芯片封装类型:BGA(球栅阵列)封装、SO类型封装等。

一般来说,SPGA封装,适用于AMD K5和Cyrix MII处理器;CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)封装,适用于Intel Pentium MMX、AMD K6、AMD K6-2、AMD K6 III、VIA Cyrix III、Cyrix/IBM 6x86MX、IDT WinChip C6和IDT WinChip 2处理器;PPGA(塑料针状矩阵Plastic Pin Grid Array)封装,适用于Intel Celeron处理器(Socket 370);FC-PGA(Flip Chip Pin Grid Array,反转芯片针脚栅格阵列)封装,适用于Coppermine系列Pentium Ⅲ、Celeron II和Pentium4处理器。SMD封装是表面贴装技术(SMT)中较常用的封装形式。重庆PCBA板特种封装流程

在制作 MOS 管之后,需要给 MOS 管芯片加上一个外壳,这就是 MOS 管封装。江西防爆特种封装定制

有核和无核封装基板,有核封装基板在结构上主要分为两个部分,中间部分为芯板,上下部分为积层板。有核封装基板制作技术是基于高密度互连(HDI)印制电路板制作技术及其改良技术。无核基板,也叫无芯基板,是指去除了芯板的封装基板。新型无核封装基板制作主要通过自下而上的电沉积技术制作出层间导电结构—铜柱。它只使用绝缘层(Build-up Layer)和铜层通过半加成(SemiAdditive Process,缩写为SAP)积层工艺实现高密度布线。积层图形制作方法:HDI,常规的HDI技术线路制作是靠减成法(蚀刻法)完成,改良型HDI技术主要是采用半加成法(电沉积铜技术)同时完成线路和微孔制作。减成法,减成法(Subtractive),在敷铜板上,通过光化学法,网印图形转移或电镀图形抗蚀层,然后蚀刻掉非图形部分的铜箔或采用机械方式去除不需要部分而制成印制电路PCB。加成法,加成法(Additive),在绝缘基材表面上,有选择性地沉积导电金属而形成导电图形的方法。江西防爆特种封装定制

上一篇: 山西专业电子产品方案市场价格

下一篇: 贵州BGA封装服务商