湖南系统级封装测试

SIP工艺解析,引线键合封装工艺工序介绍:圆片减薄,为保持一定的可操持性,Foundry出来的圆厚度一般在700um左右。封测厂必须将其研磨减薄,才适用于切割、组装,一般需要研磨到200um左右,一些叠die结构的memory封装则需研磨到50um以下。圆片切割,圆片减薄后,可以进行划片,划片前需要将晶元粘贴在蓝膜上,通过sawwing工序,将wafer切成一个 一个 单独的Dice。目前主要有两种方式:刀片切割和激光切割。芯片粘结,贴装的方式可以是用软焊料(指Pb-Sn合金,尤其是含Sn的合金)、Au—Si低共熔合金等焊接到基板上,在塑料封装中较常用的方法是使用聚合物粘结剂粘贴到金属框架上。SIP发展趋势,多样化,复杂化,密集化。湖南系统级封装测试

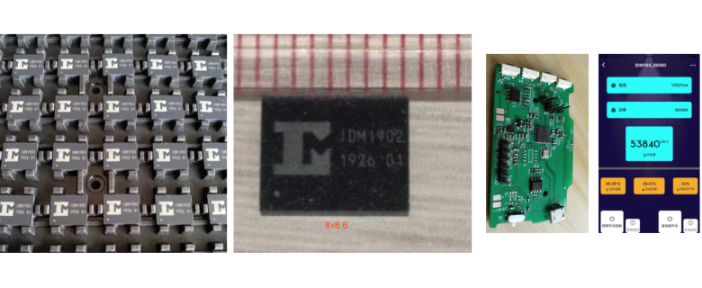

与MCM相比,SiP一个侧重点在系统,能够完成单独的系统功能。除此之外,SiP是一种集成概念,而非固定的封装结构,它可以是2D封装结构、2.5D封装结构及3D封装结构。可以根据需要采用不同的芯片排列方式和不同的内部互联技术搭配,从而实现不同的系统功能。一个典型的SiP封装芯片如图所示。采用SiP封装的芯片结构图SiP封装可以有效解决芯片工艺不同和材料不同带来的集成问题,使设计和工艺制程具有较好的灵活性。与此同时,采用SiP封装的芯片集成度高,能减少芯片的重复封装,降低布局与排线的难度,缩短研发周期。天津模组封装价位微晶片的减薄化是SiP增长面对的重要技术挑战。

SOC与SIP都是将一个包含逻辑组件、内存组件、甚至包含无源组件的系统,整合在一个单位中。区别在于SOC是从设计的角度出发,将系统所需的组件高度集成到一块芯片上;SIP是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,实现一定功能的单个标准封装件。从某种程度上说:SIP=SOC+其他(未能被集成到SOC中的芯片和组件)。SiP封装基板半导体芯片封装基板是封装测试环境的关键载体,SiP封装基板具有薄形化、高密度、高精度等技术特点,为芯片提供支撑,散热和保护,同时提供芯片与基板之间的供电和机械链接。

PoP(Package-on-Package),是用于将逻辑器件和存储器器件进行叠层封装的技术。通常情况下底层多为逻辑器件,例如移动电话基带(调制解调器)处理器或应用处理器,上层为存储器,例如闪存或者叠层内存芯片。显然,这种垂直组合封装的一个优点是节省了电路板空间。适用于需要在更小空间内实现更多功能的应用,例如数码相机、PDA、MP3 播放器和移动游戏设备等。POP的工艺流程,PoP的组装方式目前有两种。一种是预制PoP工序,即先将PoP的多层封装堆叠到一起,焊接成一个元器件,再贴装到PCB上,然后再进行一次回流焊。一种是在板PoP工序上,依次将底部的BGA和顶部BGA封装在PCB上,然后过一次回流焊。SiP 在应用终端产品领域(智能手表、TWS、手机、穿戴式产品、智能汽车)的爆发点也将愈来愈近。

SiP系统级封装需求主要包括以下几个方面:1、稳定的力控制:在固晶过程中,需要对芯片施加一定的压力以确保其与基板之间的良好连接。然而,过大的压力可能导致芯片损坏,而过小的压力则可能导致连接不良。因此,固晶设备需要具备稳定的力控制能力,以确保施加在芯片上的压力恰到好处。2、温度场及变形的控制:在固晶过程中,温度的变化和基板的变形都可能影响芯片的位置和连接质量。因此,固晶设备需要具备对温度场和基板变形的控制能力,以确保在整个固晶过程中温度和变形的稳定。SiP涉及许多类型的封装技术,如超精密表面贴装技术(SMT)、封装堆叠技术,封装嵌入式技术等。辽宁BGA封装测试

固晶贴片机(Die bonder),是封装过程中的芯片贴装(Die attach)的主要设备。湖南系统级封装测试

不同类别芯片进行3D集成时,通常会把两个不同芯片竖直叠放起来,通过TSV进行电气连接,与下面基板相互连接,有时还需在其表面做RDL,实现上下TSV连接。4D SIP,4D集成定义主要是关于多块基板的方位和相互连接方式,因此在4D集成也会包含2D,2.5D,3D的集成方式。物理结构:多块基板采用非平行的方式进行安装,且每一块基板上均设有元器件,元器件的安装方式具有多样性。电气连接:基板间采用柔性电路或焊接的方式相连,基板中芯片的电气连接多样化。湖南系统级封装测试

上一篇: 南通电力高压线太阳能测温产品方案市价

下一篇: 浙江芯片设计外包管理系统解决方案