湖南7050差分晶振

差分晶振与微处理器的连接方式

差分晶振,作为一种高性能的振荡器,以其低电平、低抖动和低功耗等特性,在现代电子设备中发挥着至关重要的作用。它

能够输出差分信号,使用两种相位完全相反的信号来消除共模噪声,从而极大地提高系统的性能。微处理器,作为计算机系统的关键,负责执行指令、处理数据以及控制其他部件的运行。其由大规模集成电路组成,包括寄存器堆、运算器、时序控制电路等,能够完成取指令、执行指令以及与外界存储器和逻辑部件交换信息等操作。差分晶振与微处理器的连接,主要是通过差分信号线与微处理器的时钟输入端口进行连接。

差分晶振输出的差分信号,经过适当的电路处理,可以直接接入微处理器的时钟系统,为微处理器提供稳定、精确的时钟信号。在连接过程中,需要注意差分信号的平衡性和对称性,以确保信号传输的稳定性和可靠性。同时,还需要考虑差分晶振的工作电压、频率范围等参数与微处理器的兼容性,以避免因不匹配而导致的性能下降或损坏。

此外,为了进一步提高系统的稳定性和抗干扰能力,还可以在差分晶振与微处理器之间加入滤波电路和隔离器件,以减小噪声干扰和电磁辐射的影响。 差分晶振的驱动电路如何设计?湖南7050差分晶振

它们的主要功能是为系统提供稳定的时钟信号,确保设备的正常运行。

差分晶振的可靠性主要取决于其材料和设计。高质量的材料能够抵抗恶劣的工作环境,如高温、低温、高湿度等,从而保证晶振的稳定运行。此外,先进的设计也可以提高差分晶振的可靠性。例如,一些差分晶振采用了抗震设计,能够抵抗外部冲击和振动,避免因机械应力引起的故障。

在差分晶振的生产过程中,质量控制也是保证可靠性的重要环节。通过严格的生产流程和检测标准,可以确保每一个出厂的差分晶振都达到了预定的性能标准。此外,长期的老化测试和环境适应性测试也是评估差分晶振可靠性的重要手段。

除了材料和设计,差分晶振的可靠性还与其应用领域和使用环境密切相关。在一些对时间精度要求极高的应用中,如通信、雷达等,差分晶振的可靠性尤为重要。在这些领域,差分晶振的微小偏差都可能导致系统性能的严重下降。

总的来说,差分晶振的可靠性非常高,但这并不意味着它们可以适用于所有场合。在选择差分晶振时,需要根据具体的应用需求和使用环境来综合考虑其性能、可靠性和成本等因素。同时,对于已经投入使用的差分晶振,定期的维护和检测也是保证其长期稳定运行的关键。 海南5032差分晶振差分晶振的相位抖动如何?

差分晶振,作为一种高精度、高稳定性的振荡器,广泛应用于各种电子设备中,起到提供稳定频率源的重要作用。尤其在高温环境下,差分晶振的性能表现尤为关键。那么,差分晶振在高温环境下的性能如何呢?首先,我们需要了解高温环境对电子设备的影响。高温会加速电子设备的老化,可能导致电路中的元器件性能下降,从而影响到设备的正常运行。而差分晶振作为电子设备中的关键元件,其性能稳定性对设备的正常运行至关重要。在高温环境下,差分晶振的性能表现非常稳定。由于其内部采用了特殊的材料和结构设计,差分晶振能够在高温环境下保持其振荡频率的稳定性和准确性。同时,差分晶振还具有优异的温度特性,能够在高温环境下长期稳定运行,不会出现明显的频率漂移或相位变化。此外,差分晶振还具有较好的抗干扰能力。在高温环境下,设备可能受到各种电磁干扰的影响,而差分晶振的差分输出方式能够有效地抑制共模干扰,保证信号的纯净度和稳定性。综上所述,差分晶振在高温环境下的性能表现非常优异。其稳定的振荡频率、准确的输出信号以及良好的抗干扰能力,使得差分晶振在高温环境下能够保持设备的正常运行,为各种电子设备在高温环境下的稳定运行提供了有力的保障。

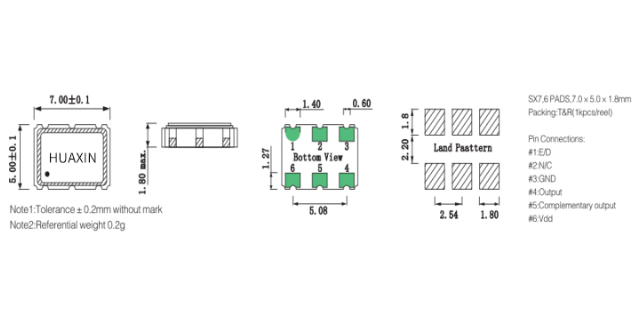

LVDS(LowVoltageDifferentialSignaling,低电压差分信号)接口,又称为RS-644总线接口,是20世纪90年代提出的一种数据传输和接口技术。它克服了TTL电平方式在传输宽带高码率数据时功耗大、电磁干扰大的问题。采用低压和低电流驱动方式,实现了低噪声和低功耗,因此在液晶电视等需要高信号完整性和低抖动的系统中得到了广泛应用。CML(CurrentModeLogic,电流模式逻辑)则是一种常用于网络物理层传输和高速Serdes器件的接口技术。其理论极限速度可达10Gbit/s,功率更低,外部更简单。CML的输出电路形式是一个差分对,输出信号的摆幅与供电电压有关,耦合方式则根据接收器和发送器的电源配置来选择。LVPECL(LowVoltagePositiveEmitter-CoupledLogic,低电压正射极耦合逻辑)接口由ECL和PECL发展而来,使用3.3V电平。其输出结构为一对差分信号,通过电流源接地。LVPECL的差分输出端具有特定的传输阻抗和输出电平,使其在各种应用场景中都能保持稳定的性能。VML(VoltageModeLogic,电压模式逻辑)接口则具有其独特的电压特性和信号传输方式,为不同设备间的连接提供了灵活的选择。这四种接口技术各具特色,为现代电子设备提供了高效、稳定的数据传输方案。差分晶振与数字电路之间的接口设计需要注意哪些问题?

差分晶振与FPGA的连接方式及应用

差分晶振以其独特的差分信号输出方式,有效地消除了共模噪声,实现了高性能的系统运行。而FPGA,作为现场可编程门阵列,具备高度的灵活性和可配置性,使得其在各种应用场景中都能发挥出色性能。那么,差分晶振如何与FPGA进行连接呢?

首先,差分晶振的输出为差分信号,因此在与FPGA连接时,需要确保FPGA的输入端口能够接收差分信号。这通常意味着需要使用FPGA上的差分输入接收器(DifferentialInputReceiver)来实现与差分晶振的连接。连接时,差分晶振的正负两根信号线应分别接入FPGA的差分输入接收器的对应引脚。这种连接方式可以有效地保证差分信号的完整性,避免因信号传输过程中的噪声干扰而影响系统的性能。

在连接过程中,还需要注意差分晶振的工作电压和频率等参数与FPGA的兼容性。确保差分晶振的电源电压、工作频率等参数在FPGA的接受范围内,以确保连接的稳定性和可靠性。差分晶振与FPGA的连接,不仅使得系统能够获得稳定、准确的时钟信号,而且还可以通过FPGA的编程能力,实现对时钟信号的灵活处理和控制。这使得差分晶振与FPGA的组合在各种需要高性能时钟源的应用场景中,如通信、数据处理等领域,具有广泛的应用前景。

差分晶振与普通晶振有何区别?海南5032差分晶振

差分晶振如何与FPGA连接?湖南7050差分晶振

差分晶振的自动相位控制(APC)功能解析

差分晶振独特的差分结构使其具有优异的抗干扰能力和温度稳定性。然而,差分晶振的性能表现,很大程度上取决于其自动相位控制(APC)功能的实现。自动相位控制(APC)是差分晶振的一项关键功能,它通过自动调整振荡器的相位,保证输出的稳定性和准确性。APC功能的实现,依赖于精密的电路设计和算法控制。在差分晶振工作过程中,APC功能能够实时监测振荡器的相位变化,一旦发现偏差,就会立即启动调整机制,使振荡器迅速恢复到正确的相位状态。这种自动调整的能力,使得差分晶振在各种复杂的工作环境下,都能保持稳定的输出。无论是温度变化、电源波动,还是外部干扰,APC功能都能有效地进行相位调整,确保差分晶振的性能不受影响。此外,APC功能还具有很高的响应速度。一旦检测到相位偏差,它能在极短的时间内完成调整,保证差分晶振的输出始终与设定值保持一致。这种快速响应的特性,使得差分晶振在需要高精度、高稳定性输出的应用中,具有不可替代的优势。

总的来说,差分晶振的自动相位控制(APC)功能是其性能稳定、精度高的重要保障。它使差分晶振在各种工作环境下,都能保持稳定的输出,满足各种高精度、高稳定性要求的应用需求。 湖南7050差分晶振

上一篇: 厂家有源晶振频率

下一篇: 广西321532.768KHZ晶振