上海压电半导体器件加工方案

半导体技术进入纳米时代后,除了水平方向尺寸的微缩造成对微影技术的严苛要求外,在垂直方向的要求也同样地严格。一些薄膜的厚度都是1~2纳米,而且在整片上的误差小于5%。这相当于在100个足球场的面积上要很均匀地铺上一层约1公分厚的泥土,而且误差要控制在0.05公分的范围内。蚀刻:另外一项重要的单元制程是蚀刻,这有点像是柏油路面的刨土机或钻孔机,把不要的薄层部分去除或挖一个深洞。只是在半导体制程中,通常是用化学反应加上高能的电浆,而不是用机械的方式。在未来的纳米蚀刻技术中,有一项深度对宽度的比值需求是相当于要挖一口100公尺的深井,挖完之后再用三种不同的材料填满深井,可是每一层材料的厚度只有10层原子或分子左右。这也是技术上的一大挑战。微机电系统是微电路和微机械按功能要求在芯片上的集成,尺寸通常在毫米或微米级。上海压电半导体器件加工方案

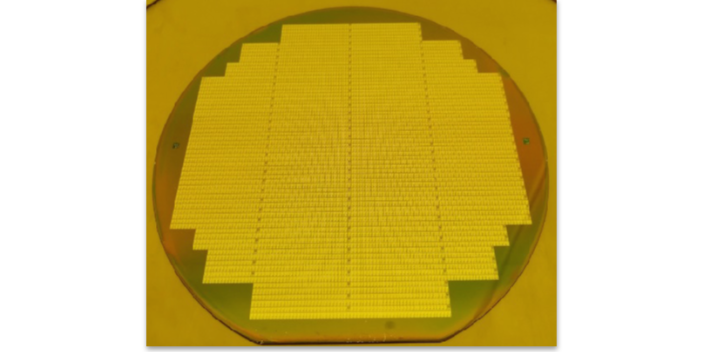

纳米技术有很多种,基本上可以分成两类,一类是由下而上的方式或称为自组装的方式,另一类是由上而下所谓的微缩方式。前者以各种材料、化工等技术为主,后者则以半导体技术为主。以前我们都称 IC 技术是「微电子」技术,那是因为晶体管的大小是在微米(10-6米)等级。但是半导体技术发展得非常快,每隔两年就会进步一个世代,尺寸会缩小成原来的一半,这就是有名的摩尔定律(Moore’s Law)。到了 2001 年,晶体管尺寸甚至已经小于 0.1 微米,也就是小于 100 纳米。因此是纳米电子时代,未来的 IC 大部分会由纳米技术做成。但是为了达到纳米的要求,半导体制程的改变须从基本步骤做起。每进步一个世代,制程步骤的要求都会变得更严格、更复杂。上海压电半导体器件加工方案半导体器件加工的目标是在晶圆上制造出各种功能的电子元件。

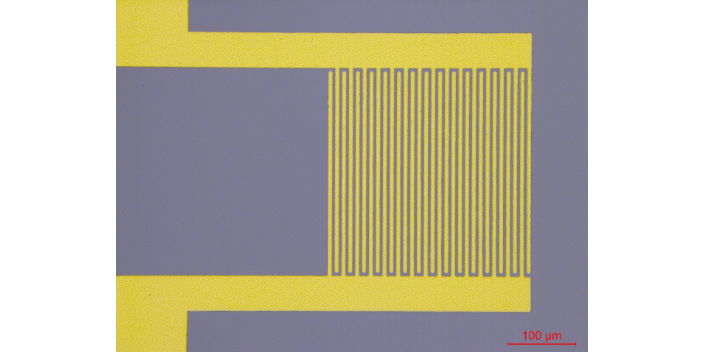

刻蚀在半导体器件加工中的作用主要有以下几个方面:1. 图案转移:刻蚀可以将光刻胶或光刻层上的图案转移到半导体材料表面。光刻胶是一种光敏材料,通过光刻曝光和显影等工艺,可以形成所需的图案。刻蚀可以将光刻胶上的图案转移到半导体材料表面,形成电路结构、纳米结构和微细结构等。2. 电路形成:刻蚀可以将半导体材料表面的杂质、氧化物等去除,形成电路结构。在半导体器件加工中,刻蚀常用于形成晶体管的栅极、源极和漏极等结构,以及形成电容器的电极等。

半导体技术挑战:除了精确度与均匀度的要求外,在量产时对于设备还有一项严苛的要求,那就是速度。因为时间就是金钱,在同样的时间内,如果能制造出较多的成品,成本自然下降,价格才有竞争力。另外质量的稳定性也非常重要,不只同一批产品的质量要一样,现在生产的IC与下星期、下个月生产的也要具有同样的性能,因此质量管控非常重要。通常量产工厂对于生产条件的管制,包括原料、设备条件、制程条件与环境条件等要求都非常严格,不容任意变更,为的就是保持质量的稳定度。按照被刻蚀的材料类型来划分,干法刻蚀主要分成三种:金属刻蚀、介质刻蚀和硅刻蚀。

光刻技术在半导体器件加工中起着至关重要的作用。它可以实现图案转移、提高分辨率、制造多层结构、控制器件性能、提高生产效率和降低成本。随着半导体器件的不断发展,光刻技术也在不断创新和改进,以满足更高的制造要求。刻蚀在半导体器件加工中起着至关重要的作用。它是一种通过化学或物理方法去除材料表面的工艺,用于制造微电子器件中的电路结构、纳米结构和微细结构。刻蚀可以实现高精度、高分辨率的图案转移,从而实现半导体器件的功能。表面硅MEMS加工技术是在集成电路平面工艺基础上发展起来的一种MEMS工艺技术。上海压电半导体器件加工方案

在热处理的过程中,晶圆上没有增加或减去任何物质,另外会有一些污染物和水汽从晶圆上蒸发。上海压电半导体器件加工方案

半导体器件加工是指将半导体材料加工成具有特定功能的器件的过程。它是半导体工业中非常重要的一环,涉及到多个步骤和工艺。下面将详细介绍半导体器件加工的步骤。蚀刻:蚀刻是将光刻图案转移到晶圆上的关键步骤。蚀刻是利用化学反应将不需要的材料从晶圆表面去除的过程。常用的蚀刻方法包括湿蚀刻和干蚀刻。沉积:沉积是在晶圆表面上形成薄膜的过程。沉积可以通过物理的气相沉积(PVD)、化学气相沉积(CVD)、溅射沉积等方法实现。沉积的薄膜可以用于形成导电层、绝缘层或金属层等。上海压电半导体器件加工方案