浙江系统级封装供应

SiP还具有以下更多优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。SiP并没有一定的结构形态,芯片的排列方式可为平面式2D装和立体式3D封装。浙江系统级封装供应

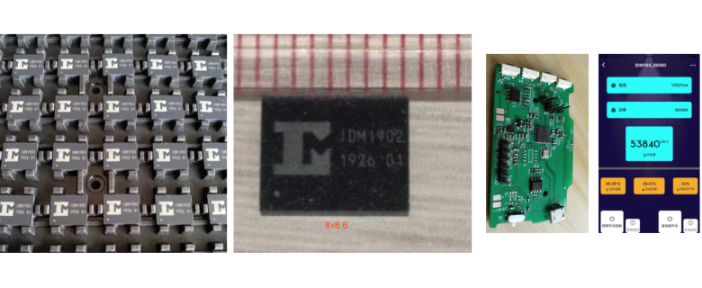

合封电子的功能,性能提升,合封电子:通过将多个芯片或模块封装在一起,云茂电子可以明显提高数据处理速度和效率。由于芯片之间的连接更紧密,数据传输速度更快,从而提高了整体性能。稳定性增强,合封电子:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,云茂电子可以减少故障率。功耗降低、开发简单,合封电子:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,云茂电子可以降低整个系统的功耗。此外,通过优化内部连接和布局,可以进一步降低功耗。防抄袭,多个芯片和元器件模块等合封在一起,就算被采购,也无法模仿抄袭。陕西模组封装供应商SiP (System in Package, 系统级封装)主要应用于消费电子、无线通信、汽车电子等领域。

SMT制程在SIP工艺流程中的三部分都有应用:1st SMT PCB贴片 + 3rd SMT FPC贴镍片 + 4th SMT FPC+COB。SiP失效模式和失效机理,主要失效模式:(1) 焊接异常:IC引脚锡渣、精密电阻连锡。Ø 原因分析:底部UF (Underfill底部填充)胶填充不佳,导致锡进入IC引脚或器件焊盘间空洞造成短路。(2) 机械应力损伤:MOS芯片、电容裂纹。Ø 原因分析:(1) SiP注塑后固化过程产生的应力;(2)设备/治具产生的应力。(3) 过电应力损伤:MOS、电容等器件EOS损伤。Ø 原因分析:PCM SiP上的器件受电应力损伤(ESD、测试设备浪涌等)。

SiP还具有以下更多优势:可靠性 – 由于SiP与使用分立元件(如IC或无源器件)的PCB系统非常相似,因此它们至少具有相同的预期故障概率。额外的可靠性来自所涉及的封装,这可以增强系统并为设备提供更长的使用寿命。一个例子是使用模塑来封装系统,从而保护焊点免受物理应力的影响。天线集成 – 在许多无线应用(蓝牙、WiFi)中,都需要天线。在系统级封装解决方案中,天线可以集成到封装中,与RF IC的距离非常短,从而确保无线解决方案的更高性能。但是,对于完整的视图,我们必须承认SiP也可能有一些缺点。SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术。

随着物联网时代越来越深入人心,不断的开发和研究有助于使SiP更接近SoC,降低成本,减少批量要求和初始投资,并在系统简化方面呈现积极趋势。此外,制造越来越大的单片SoC的推动力开始在设计验证和可制造性方面遇到障碍,因为拥有更大的芯片会导致更大的故障概率,从而造成更大的硅晶圆损失。从IP方面来看,SiP是SoC的未来替代品,因为它们可以集成较新的标准和协议,而无需重新设计。此外,SiP方法允许更快、更节能的通信和电力输送,这是在考虑Si应用的长期前景时另一个令人鼓舞的因素。微晶片的减薄化是SiP增长面对的重要技术挑战。上海MEMS封装定制

SiP 可以将多个具有不同功能的有源电子元件与可选无源器件。浙江系统级封装供应

不同类别芯片进行3D集成时,通常会把两个不同芯片竖直叠放起来,通过TSV进行电气连接,与下面基板相互连接,有时还需在其表面做RDL,实现上下TSV连接。4D SIP,4D集成定义主要是关于多块基板的方位和相互连接方式,因此在4D集成也会包含2D,2.5D,3D的集成方式。物理结构:多块基板采用非平行的方式进行安装,且每一块基板上均设有元器件,元器件的安装方式具有多样性。电气连接:基板间采用柔性电路或焊接的方式相连,基板中芯片的电气连接多样化。浙江系统级封装供应

上一篇: 浙江半导体WMS系统市场价格

下一篇: 河北专业特种封装供应商