深圳芯片封装价格

系统级封装(SiP)是将多个集成电路(IC)和无源元件捆绑到单个封装中,在单个封装下它们协同工作的方法。这与片上系统(SoC)形成鲜明对比,功能则集成到同一个芯片中。将基于各种工艺节点(CMOS,SiGe,BiCMOS)的不同电路的硅芯片可以垂直或并排堆叠在衬底上。该封装由内部接线进行连接,将所有芯片连接在一起形成一个功能系统。系统级封装类似于片上系统(SOC),但它的集成度较低,并且使用的不是单一半导体制造工艺。常见的SiP解决方案可以利用多种封装技术,例如倒装芯片、引线键合、晶圆级封装等。封装在系统中的集成电路和其他组件的数量可变,理论上是无限的,因此,工程师基本上可以将整个系统集成到单个封装中。不同的芯片,排列方式,与不同内部结合技术搭配,使SiP 的封装形态产生多样化的组合。深圳芯片封装价格

几种类型的先进封装技术:首先就是 SiP,随着 5G 的部署加快,这类封装技术的应用范围将越来越普遍。其次是应用于 Chiplet SiP 的 2.5D/3D 封装,以及晶圆级封装,并且利用晶圆级技术在射频特性上的优势推进扇出型(Fan-Out)封装。很多半导体厂商都有自己的 SiP 技术,命名方式各有不同。比如,英特尔叫 EMIB、台积电叫 SoIC。这些都是 SiP 技术,差别就在于制程工艺。在智能手机领域,除射频模块外,通用单元电路小型化需求正推升 SiP 技术的采用率;可穿戴领域,已经有在耳机和智能手表上应用 SiP 技术。深圳芯片封装价格SIP模组尺寸小,在相同功能上,可将多种芯片集成在一起,相对单独封装的IC更能节省PCB的空间。

晶圆级封装(WLP):1、定义,在晶圆原有状态下重新布线,然后用树脂密封,再植入锡球引脚,然后划片将其切割成芯片,从而制造出真实芯片大小的封装。注:重新布线是指在后段制程中,在芯片表面形成新的布线层。2、优势,传统封装中,将芯片装进封装中的时候,封装的尺寸都要大于芯片尺寸。WLP技术的优势是能够实现几乎与芯片尺寸一样大小的封装。不只芯片是批量化制造,而且封装也是批量化制造,可以较大程度上降低成本。WLP技术使用倒装焊技术(FCB),所以被称为FBGA(Flip Chip类型的BGA),芯片被称为晶圆级CSP(Chip Size Package)。工艺流程,晶圆级封装工艺流程:① 再布线工程(形成重新布线层的层间绝缘膜[中间介质层]);② 形成通孔和重新布线层(用来连接芯片和外部端子);③ 形成铜柱,并在铜柱上面生成凸点;④ 用树脂密封,再形成焊球并用划片机切割成所需的芯片。

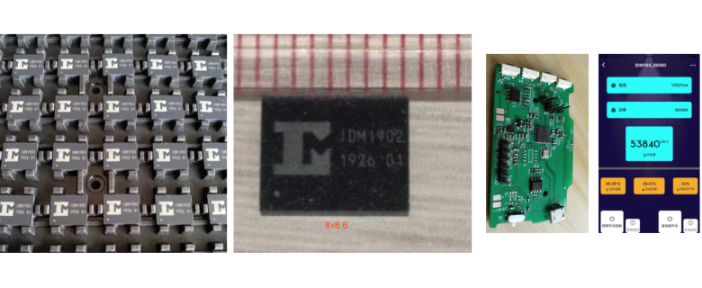

SIP工艺解析:表面打标,打标就是在封装模块的顶表面印上去不掉的、字迹清楚的字母和标识,包括制造商的信息、国家、器件代码等,主要介绍激光印码。测试,它利用测试设备(Testing Equipment)以及自动分选器(Handler),测定封装IC的电气特性,把良品、不良品区分开来;对某些产品,还要根据测试结果进行良品的分级。测试按功能可分为DC测试(直流特性)、AC测试(交流特性或timing特性)及FT测试(逻辑功能测试)三大类。同时还有一些辅助工序,如BT老化、插入、拔出、实装测试、电容充放电测试等。SiP封装基板具有薄形化、高密度、高精度等技术特点。

合封芯片、芯片合封和SiP系统级封装经常被提及的概念。但它们是三种不同的技术,还是同一种技术的不同称呼?本文将帮助我们更好地理解它们的差异。合封芯片与SiP系统级封装的定义,首先合封芯片和芯片合封都是一个意思,合封芯片是一种将多个芯片(多样选择)或不同的功能的电子模块(LDO、充电芯片、射频芯片、mos管)封装在一起的定制化芯片,从而形成一个系统或者子系统。以实现更复杂、更高效的任务。合封芯片可定制组成方式包括CoC封装技术、SiP封装技术等。SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术。陕西陶瓷封装厂商

SiP封装方法的应用领域逐渐扩展到工业控制、智能汽车、云计算、医疗电子等许多新兴领域。深圳芯片封装价格

SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术,封装成型可依据客户设计制作不同形状模块,甚至是3D立体结构,藉此可将整体尺寸缩小,预留更大空间放置电池,提供更大电力储存,延长产品使用时间,但功能更多、速度更快,因此特别适用于射频相关应用如5G毫米波模块、穿戴式装置及汽车电子等领域。微小化制程三大关键技术,在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的较主要关键。要能够实现微小化,较重要的莫过于三项制程技术:塑封、屏蔽及高密度打件技术。深圳芯片封装价格

上一篇: 北京多用途信号采集控制盒产品方案供应商

下一篇: 上海封测工厂EAP系统行价