广东射频芯片后端设计

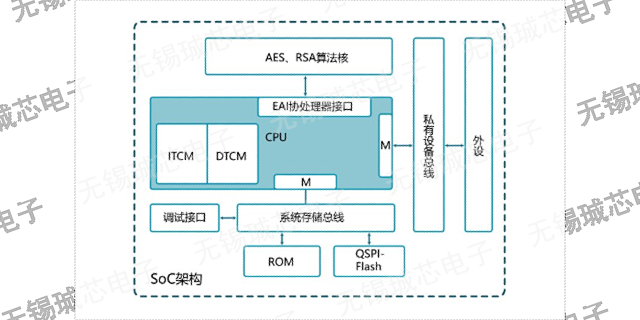

在芯片设计中集成国密算法是一项挑战,它要求设计师在保障安全性的同时,尽量不影响芯片的性能。国密算法的运行会加大芯片的计算负担,可能导致处理速度下降和功耗增加。为了解决这一问题,设计师们采用了一系列策略,包括优化算法本身的效率、改进电路设计以减少资源消耗,以及采用高效的加密模式来降低对整体性能的负面影响。此外,随着安全威胁的不断演变,算法的更新和升级也变得尤为重要。设计师们必须构建灵活的硬件平台,以便于未来的算法更新,确保长期的安全性和芯片的适应性。数字模块物理布局的合理性,直接影响芯片能否成功应对高温、高密度封装挑战。广东射频芯片后端设计

芯片国密算法是指在芯片设计中集成的较高安全级别的加密算法。随着网络安全威胁的增加,芯片国密算法的应用变得越来越重要。这些算法可以保护数据在传输和存储过程中的安全性,防止未授权的访问和篡改。芯片国密算法的设计需要考虑算法的安全性、效率和硬件实现的复杂性。随着量子计算等新技术的发展,未来的芯片国密算法将面临新的挑战和机遇。国密算法的硬件实现要求设计师不要有深厚的密码学知识,还要有精湛的电路设计技能,以确保算法能够在芯片上高效、安全地运行。湖北SARM芯片性能数字芯片广泛应用在消费电子、工业控制、汽车电子等多个行业领域。

为了提高协同效率,设计团队通常会采用集成的设计流程和工具,这些工具可以支持信息的无缝传递和实时更新。通过这种方式,任何设计上的调整都能迅速反映在整个团队中,减少了返工和延误的风险。此外,定期的审查会议和共享的设计数据库也是促进前后端设计协同的有效手段。 良好的协同工作能够提升设计的整体质量,避免因误解或沟通不畅导致的性能问题。同时,它还能加快设计流程,降低成本,使产品能够更快地进入市场,满足客户需求。在竞争激烈的半导体市场中,这种协同工作的能力往往成为企业能否快速响应市场变化和用户需求的关键因素。

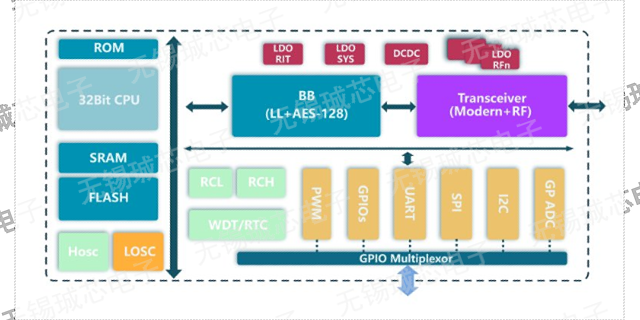

芯片运行功耗是芯片设计中的一个重要考虑因素,它直接影响到设备的电池寿命、散热需求和成本。随着芯片性能的不断提升,功耗管理变得越来越具有挑战性。设计师们采取多种策略来降低功耗,包括使用更低的电压、更高效的电路设计、动态电压频率调整(DVFS)和电源门控等技术。此外,新的制程技术如FinFET和FD-SOI也在帮助降低功耗。这些技术的应用不提高了芯片的性能,同时也使得设备更加节能,对于推动移动设备和高性能计算的发展具有重要作用。精细化的芯片数字木块物理布局,旨在限度地提升芯片的性能表现和可靠性。

芯片设计流程是一个系统化、多阶段的过程,它从概念设计开始,经过逻辑设计、物理设计、验证和测试,终到芯片的制造。每个阶段都有严格的要求和标准,需要多个专业团队的紧密合作。芯片设计流程的管理非常关键,它涉及到项目规划、资源分配、风险管理、进度控制和质量保证。随着芯片设计的复杂性增加,设计流程的管理变得越来越具有挑战性。有效的设计流程管理可以缩短设计周期、降低成本、提高设计质量和可靠性。为了应对这些挑战,设计团队需要采用高效的项目管理方法和自动化的设计工具。芯片设计前期需充分考虑功耗预算,以满足特定应用场景的严苛要求。广东射频芯片后端设计

网络芯片在云计算、数据中心等场景下,确保了海量数据流的实时交互与传输。广东射频芯片后端设计

芯片的运行功耗是其设计中的关键指标之一,直接关系到产品的市场竞争力和用户体验。随着移动设备和数据中心对能效的高要求,芯片设计者们正致力于通过各种技术降低功耗。这些技术包括使用先进的制程技术、优化电源管理、采用低功耗设计策略以及开发新型的电路架构。功耗优化是一个系统工程,需要在设计初期就进行细致规划,并贯穿整个设计流程。通过精细的功耗管理,设计师能够在不放弃性能的前提下,提升设备的电池寿命和用户满意度。广东射频芯片后端设计